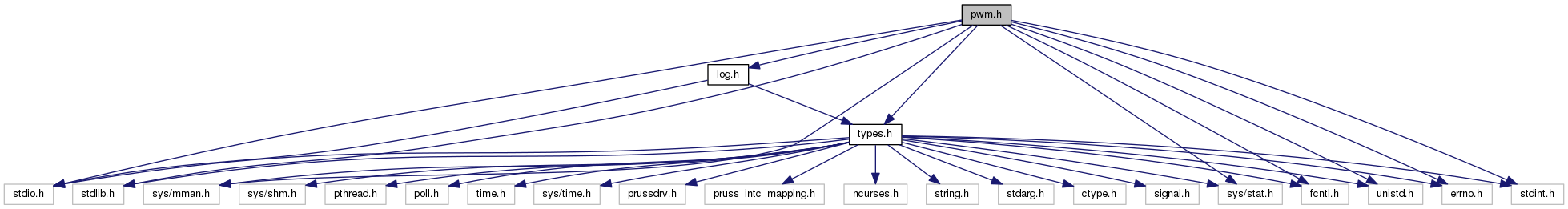

#include <stdio.h>#include <stdlib.h>#include <sys/mman.h>#include <sys/stat.h>#include <fcntl.h>#include <unistd.h>#include <errno.h>#include <stdint.h>#include "types.h"#include "log.h" Include dependency graph for pwm.h:

Include dependency graph for pwm.h: This graph shows which files directly or indirectly include this file:

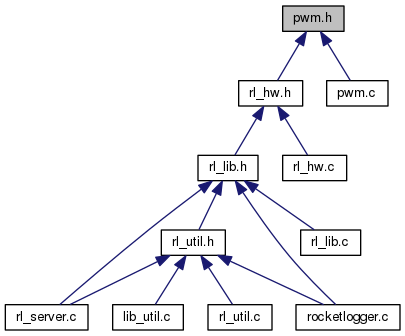

This graph shows which files directly or indirectly include this file:Go to the source code of this file.

Macros | |

| #define | PWMSS0_BASE 0x48300000 |

| PWMSS0 register base address. More... | |

| #define | PWMSS1_BASE 0x48302000 |

| PWMSS1 register base address. More... | |

| #define | EPWM_OFFSET 0x0200 |

| EPWM module register offset. More... | |

| #define | PWM_SIZE 0x00000FFF |

| Size of PWM register memory. More... | |

| #define | TBCTL (EPWM_OFFSET+0x0) / sizeof (uint16_t) |

| Counter control register offset. More... | |

| #define | TBPRD (EPWM_OFFSET+0xA) / sizeof (uint16_t) |

| Period register offset. More... | |

| #define | CMPA (EPWM_OFFSET+0x12) / sizeof (uint16_t) |

| Compare register A offset. More... | |

| #define | CMPB (EPWM_OFFSET+0x14) / sizeof (uint16_t) |

| Compare register B offset. More... | |

| #define | AQCTLA (EPWM_OFFSET+0x16) / sizeof (uint16_t) |

| Action qualifier register offset. More... | |

| #define | AQCTLB (EPWM_OFFSET+0x18) / sizeof (uint16_t) |

| Action qualifier register B offset. More... | |

| #define | TBCTL_DEFAULT 0xC000 |

| Default counter value (see AM335x_TR) More... | |

| #define | UP_DOWN_COUNT 0x0002 |

| Up-down counting. More... | |

| #define | PRESCALE2 0x0400 |

| Counter prescale 2. More... | |

| #define | RWC_AQ_A 0x0060 |

| Action qualifier A value for latch reset (see AM335x_TR) More... | |

| #define | RWC_AQ_B 0x0900 |

| Action qualifier B value for latch reset (see AM335x_TR) More... | |

| #define | PULSE_WIDTH 0.1 |

| Latch reset pulse width (part of sampling period) More... | |

| #define | MARGIN 0.1 |

| Latch reset period margin. More... | |

| #define | PWM_PERIOD_SCALE 50000000 * (1 + PULSE_WIDTH + MARGIN) |

| Latch reset period scaling factor. More... | |

| #define | ADC_CLOCK_PERIOD 48 |

| ADC master clock period in ns. More... | |

| #define | ADC_AQ 0x0025 |

| Action qualifier value for ADC clock (see AM335x_TR) More... | |

Functions | |

| int | pwm_setup (void) |

| void | pwm_close (void) |

| void | range_clock_setup (int sample_rate) |

| void | adc_clock_setup (void) |

Macro Definition Documentation

| #define ADC_AQ 0x0025 |

Action qualifier value for ADC clock (see AM335x_TR)

Definition at line 71 of file pwm.h.

Referenced by adc_clock_setup().

| #define ADC_CLOCK_PERIOD 48 |

ADC master clock period in ns.

Definition at line 69 of file pwm.h.

Referenced by adc_clock_setup().

| #define AQCTLA (EPWM_OFFSET+0x16) / sizeof (uint16_t) |

Action qualifier register offset.

Definition at line 39 of file pwm.h.

Referenced by adc_clock_setup(), and range_clock_setup().

| #define AQCTLB (EPWM_OFFSET+0x18) / sizeof (uint16_t) |

Action qualifier register B offset.

Definition at line 41 of file pwm.h.

Referenced by range_clock_setup().

| #define CMPA (EPWM_OFFSET+0x12) / sizeof (uint16_t) |

Compare register A offset.

Definition at line 35 of file pwm.h.

Referenced by adc_clock_setup(), and range_clock_setup().

| #define CMPB (EPWM_OFFSET+0x14) / sizeof (uint16_t) |

| #define PRESCALE2 0x0400 |

| #define PULSE_WIDTH 0.1 |

Latch reset pulse width (part of sampling period)

Definition at line 60 of file pwm.h.

Referenced by range_clock_setup().

| #define PWM_PERIOD_SCALE 50000000 * (1 + PULSE_WIDTH + MARGIN) |

Latch reset period scaling factor.

Definition at line 64 of file pwm.h.

Referenced by range_clock_setup().

| #define PWM_SIZE 0x00000FFF |

Size of PWM register memory.

Definition at line 27 of file pwm.h.

Referenced by pwm_close(), and pwm_setup().

| #define PWMSS0_BASE 0x48300000 |

PWMSS0 register base address.

Copyright (c) 2016-2017, ETH Zurich, Computer Engineering Group

Definition at line 19 of file pwm.h.

Referenced by pwm_setup().

| #define PWMSS1_BASE 0x48302000 |

| #define RWC_AQ_A 0x0060 |

Action qualifier A value for latch reset (see AM335x_TR)

Definition at line 54 of file pwm.h.

Referenced by range_clock_setup().

| #define RWC_AQ_B 0x0900 |

Action qualifier B value for latch reset (see AM335x_TR)

Definition at line 56 of file pwm.h.

Referenced by range_clock_setup().

| #define TBCTL (EPWM_OFFSET+0x0) / sizeof (uint16_t) |

Counter control register offset.

Definition at line 31 of file pwm.h.

Referenced by adc_clock_setup(), and range_clock_setup().

| #define TBCTL_DEFAULT 0xC000 |

Default counter value (see AM335x_TR)

Definition at line 45 of file pwm.h.

Referenced by adc_clock_setup(), and range_clock_setup().

| #define TBPRD (EPWM_OFFSET+0xA) / sizeof (uint16_t) |

Period register offset.

Definition at line 33 of file pwm.h.

Referenced by adc_clock_setup(), and range_clock_setup().

| #define UP_DOWN_COUNT 0x0002 |

Function Documentation

| void adc_clock_setup | ( | void | ) |

Setup PWMSS0 for ADC master clock

Definition at line 84 of file pwm.c.

References ADC_AQ, ADC_CLOCK_PERIOD, AQCTLA, CMPA, pwmss0_regs, TBCTL, TBCTL_DEFAULT, and TBPRD.

Referenced by hw_init().

| void pwm_close | ( | void | ) |

Unmap PWM registers from user space

Definition at line 48 of file pwm.c.

References mem_fd, PWM_SIZE, pwmss0_regs, and pwmss1_regs.

Referenced by hw_close().

| int pwm_setup | ( | void | ) |

Map PWM registers into user space (on pwmss0_regs and pwmss1_regs pointer)

Definition at line 18 of file pwm.c.

References ERROR, FAILURE, mem_fd, PWM_SIZE, PWMSS0_BASE, pwmss0_regs, PWMSS1_BASE, pwmss1_regs, rl_log(), and SUCCESS.

Referenced by hw_init().

Here is the call graph for this function:

Here is the call graph for this function:| void range_clock_setup | ( | int | sample_rate | ) |

Setup PWMSS1 for range latch reset clock

- Parameters

-

sample_rate ADC sampling rate in Sps

Definition at line 64 of file pwm.c.

References AQCTLA, AQCTLB, CMPA, CMPB, PRESCALE2, PULSE_WIDTH, PWM_PERIOD_SCALE, pwmss1_regs, RWC_AQ_A, RWC_AQ_B, TBCTL, TBCTL_DEFAULT, TBPRD, and UP_DOWN_COUNT.

Referenced by hw_init().