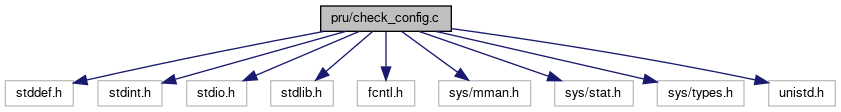

#include <stddef.h>#include <stdint.h>#include <stdio.h>#include <stdlib.h>#include <fcntl.h>#include <sys/mman.h>#include <sys/stat.h>#include <sys/types.h>#include <unistd.h> Include dependency graph for check_config.c:

Include dependency graph for check_config.c:Go to the source code of this file.

Macros | |

| #define | CM_PER_BASE 0x44E00000 |

| CM_PER register base address. More... | |

| #define | CM_PER_SIZE 0x0400 |

| #define | L4LS_CLKSTCTRL_OFFSET 0x00 |

| #define | L4LS_CLKCTRL_OFFSET 0x60 |

| #define | EPWMSS1_CLKCTRL_OFFSET 0xCC |

| #define | EPWMSS0_CLKCTRL_OFFSET 0xD4 |

| #define | EPWMSS2_CLKCTRL_OFFSET 0xD8 |

| #define | PRU_ICSS_CLKCTRL_OFFSET 0xE8 |

| #define | CONTROL_BASE 0x44E10000 |

| CONTROL register base address. More... | |

| #define | CONTROL_SIZE 0x20000 |

| #define | PWMSS_CTRL_OFFSET 0x664 |

| #define | PWM0_BASE 0x48300000 |

| PWM0 register base address. More... | |

| #define | PWM1_BASE 0x48302000 |

| PWM1 register base address. More... | |

| #define | PWM2_BASE 0x48304000 |

| PWM2 module base address. More... | |

| #define | PWMSS_OFFSET 0x0000 |

| PWMSS module register offset. More... | |

| #define | ECAP_OFFSET 0x0100 |

| eCAP module register offset More... | |

| #define | EQEP_OFFSET 0x0180 |

| eQEP module register offset More... | |

| #define | EPWM_OFFSET 0x0200 |

| ePWM module register offset More... | |

| #define | PWM_SIZE 0x0260 |

| PWM module register map size. More... | |

| #define | PWMSS_SIZE 0x0100 |

| PWMSS module register map size. More... | |

| #define | ECAP_SIZE 0x0080 |

| eCAP module register map size More... | |

| #define | EQEP_SIZE 0x0080 |

| eQEP module register map size More... | |

| #define | EPWM_SIZE 0x0060 |

| ePWM module register map size More... | |

| #define | PWMSS0_BASE (PWM0_BASE + PWMSS_OFFSET) |

| PWMSS0 register base address. More... | |

| #define | PWMSS1_BASE (PWM1_BASE + PWMSS_OFFSET) |

| PWMSS1 register base address. More... | |

| #define | PWMSS2_BASE (PWM2_BASE + PWMSS_OFFSET) |

| PWMSS2 module register offset. More... | |

| #define | EPWM0_BASE (PWM0_BASE + EPWM_OFFSET) |

| ePWM0 register base address More... | |

| #define | EPWM1_BASE (PWM1_BASE + EPWM_OFFSET) |

| ePWM1 register base address More... | |

| #define | EPWM2_BASE (PWM2_BASE + EPWM_OFFSET) |

| ePWM2 register base address More... | |

| #define | PWMSS_IDVER_OFFSET 0x00 |

| IP Revision Register. More... | |

| #define | PWMSS_SYSCONFIG_OFFSET 0x04 |

| System Configuration Register. More... | |

| #define | PWMSS_CLKCONFIG_OFFSET 0x08 |

| Clock Configuration Register. More... | |

| #define | PWMSS_CLKSTATUS_OFFSET 0x0C |

| Clock Status Register. More... | |

| #define | EPWM_TBCTL_OFFSET 0x00 |

| Time-Base Control Register. More... | |

| #define | EPWM_TBSTS_OFFSET 0x02 |

| Time-Base Status Register. More... | |

| #define | EPWM_TBPHS_OFFSET 0x06 |

| Time-Base Phase Register. More... | |

| #define | EPWM_TBCNT_OFFSET 0x08 |

| Time-Base Counter Register. More... | |

| #define | EPWM_TBPRD_OFFSET 0x0A |

| Time-Base Period Register. More... | |

| #define | EPWM_CMPCTL_OFFSET 0x0E |

| Counter-Compare Control Register. More... | |

| #define | EPWM_CMPA_OFFSET 0x12 |

| Counter-Compare A Register. More... | |

| #define | EPWM_CMPB_OFFSET 0x14 |

| Counter-Compare B Register. More... | |

| #define | EPWM_AQCTLA_OFFSET 0x16 |

| Action-Qualifier Control Register for Output A (EPWMxA) More... | |

| #define | EPWM_AQCTLB_OFFSET 0x18 |

| Action-Qualifier Control Register for Output B (EPWMxB) More... | |

Functions | |

| int | main () |

| Program main fuction. More... | |

Macro Definition Documentation

◆ CM_PER_BASE

| #define CM_PER_BASE 0x44E00000 |

CM_PER register base address.

Copyright (c) 2016-2020, ETH Zurich, Computer Engineering Group All rights reserved.

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Definition at line 46 of file check_config.c.

◆ CM_PER_SIZE

| #define CM_PER_SIZE 0x0400 |

Definition at line 47 of file check_config.c.

◆ CONTROL_BASE

| #define CONTROL_BASE 0x44E10000 |

CONTROL register base address.

Definition at line 59 of file check_config.c.

◆ CONTROL_SIZE

| #define CONTROL_SIZE 0x20000 |

Definition at line 60 of file check_config.c.

◆ ECAP_OFFSET

| #define ECAP_OFFSET 0x0100 |

eCAP module register offset

Definition at line 75 of file check_config.c.

◆ ECAP_SIZE

| #define ECAP_SIZE 0x0080 |

eCAP module register map size

Definition at line 86 of file check_config.c.

◆ EPWM0_BASE

| #define EPWM0_BASE (PWM0_BASE + EPWM_OFFSET) |

ePWM0 register base address

Definition at line 103 of file check_config.c.

◆ EPWM1_BASE

| #define EPWM1_BASE (PWM1_BASE + EPWM_OFFSET) |

ePWM1 register base address

Definition at line 105 of file check_config.c.

◆ EPWM2_BASE

| #define EPWM2_BASE (PWM2_BASE + EPWM_OFFSET) |

ePWM2 register base address

Definition at line 107 of file check_config.c.

◆ EPWM_AQCTLA_OFFSET

| #define EPWM_AQCTLA_OFFSET 0x16 |

Action-Qualifier Control Register for Output A (EPWMxA)

Definition at line 137 of file check_config.c.

◆ EPWM_AQCTLB_OFFSET

| #define EPWM_AQCTLB_OFFSET 0x18 |

Action-Qualifier Control Register for Output B (EPWMxB)

Definition at line 139 of file check_config.c.

◆ EPWM_CMPA_OFFSET

| #define EPWM_CMPA_OFFSET 0x12 |

Counter-Compare A Register.

Definition at line 133 of file check_config.c.

◆ EPWM_CMPB_OFFSET

| #define EPWM_CMPB_OFFSET 0x14 |

Counter-Compare B Register.

Definition at line 135 of file check_config.c.

◆ EPWM_CMPCTL_OFFSET

| #define EPWM_CMPCTL_OFFSET 0x0E |

Counter-Compare Control Register.

Definition at line 131 of file check_config.c.

◆ EPWM_OFFSET

| #define EPWM_OFFSET 0x0200 |

ePWM module register offset

Definition at line 79 of file check_config.c.

◆ EPWM_SIZE

| #define EPWM_SIZE 0x0060 |

ePWM module register map size

Definition at line 90 of file check_config.c.

◆ EPWM_TBCNT_OFFSET

| #define EPWM_TBCNT_OFFSET 0x08 |

Time-Base Counter Register.

Definition at line 127 of file check_config.c.

◆ EPWM_TBCTL_OFFSET

| #define EPWM_TBCTL_OFFSET 0x00 |

Time-Base Control Register.

Definition at line 121 of file check_config.c.

◆ EPWM_TBPHS_OFFSET

| #define EPWM_TBPHS_OFFSET 0x06 |

Time-Base Phase Register.

Definition at line 125 of file check_config.c.

◆ EPWM_TBPRD_OFFSET

| #define EPWM_TBPRD_OFFSET 0x0A |

Time-Base Period Register.

Definition at line 129 of file check_config.c.

◆ EPWM_TBSTS_OFFSET

| #define EPWM_TBSTS_OFFSET 0x02 |

Time-Base Status Register.

Definition at line 123 of file check_config.c.

◆ EPWMSS0_CLKCTRL_OFFSET

| #define EPWMSS0_CLKCTRL_OFFSET 0xD4 |

Definition at line 52 of file check_config.c.

◆ EPWMSS1_CLKCTRL_OFFSET

| #define EPWMSS1_CLKCTRL_OFFSET 0xCC |

Definition at line 51 of file check_config.c.

◆ EPWMSS2_CLKCTRL_OFFSET

| #define EPWMSS2_CLKCTRL_OFFSET 0xD8 |

Definition at line 53 of file check_config.c.

◆ EQEP_OFFSET

| #define EQEP_OFFSET 0x0180 |

eQEP module register offset

Definition at line 77 of file check_config.c.

◆ EQEP_SIZE

| #define EQEP_SIZE 0x0080 |

eQEP module register map size

Definition at line 88 of file check_config.c.

◆ L4LS_CLKCTRL_OFFSET

| #define L4LS_CLKCTRL_OFFSET 0x60 |

Definition at line 50 of file check_config.c.

◆ L4LS_CLKSTCTRL_OFFSET

| #define L4LS_CLKSTCTRL_OFFSET 0x00 |

Definition at line 49 of file check_config.c.

◆ PRU_ICSS_CLKCTRL_OFFSET

| #define PRU_ICSS_CLKCTRL_OFFSET 0xE8 |

Definition at line 54 of file check_config.c.

◆ PWM0_BASE

| #define PWM0_BASE 0x48300000 |

PWM0 register base address.

Definition at line 66 of file check_config.c.

◆ PWM1_BASE

| #define PWM1_BASE 0x48302000 |

PWM1 register base address.

Definition at line 68 of file check_config.c.

◆ PWM2_BASE

| #define PWM2_BASE 0x48304000 |

PWM2 module base address.

Definition at line 70 of file check_config.c.

◆ PWM_SIZE

| #define PWM_SIZE 0x0260 |

PWM module register map size.

Definition at line 82 of file check_config.c.

◆ PWMSS0_BASE

| #define PWMSS0_BASE (PWM0_BASE + PWMSS_OFFSET) |

PWMSS0 register base address.

Definition at line 95 of file check_config.c.

◆ PWMSS1_BASE

| #define PWMSS1_BASE (PWM1_BASE + PWMSS_OFFSET) |

PWMSS1 register base address.

Definition at line 97 of file check_config.c.

◆ PWMSS2_BASE

| #define PWMSS2_BASE (PWM2_BASE + PWMSS_OFFSET) |

PWMSS2 module register offset.

Definition at line 99 of file check_config.c.

◆ PWMSS_CLKCONFIG_OFFSET

| #define PWMSS_CLKCONFIG_OFFSET 0x08 |

Clock Configuration Register.

Definition at line 115 of file check_config.c.

◆ PWMSS_CLKSTATUS_OFFSET

| #define PWMSS_CLKSTATUS_OFFSET 0x0C |

Clock Status Register.

Definition at line 117 of file check_config.c.

◆ PWMSS_CTRL_OFFSET

| #define PWMSS_CTRL_OFFSET 0x664 |

Definition at line 62 of file check_config.c.

◆ PWMSS_IDVER_OFFSET

| #define PWMSS_IDVER_OFFSET 0x00 |

IP Revision Register.

Definition at line 111 of file check_config.c.

◆ PWMSS_OFFSET

| #define PWMSS_OFFSET 0x0000 |

PWMSS module register offset.

Definition at line 73 of file check_config.c.

◆ PWMSS_SIZE

| #define PWMSS_SIZE 0x0100 |

PWMSS module register map size.

Definition at line 84 of file check_config.c.

◆ PWMSS_SYSCONFIG_OFFSET

| #define PWMSS_SYSCONFIG_OFFSET 0x04 |

System Configuration Register.

Definition at line 113 of file check_config.c.

Function Documentation

◆ main()

| int main | ( | void | ) |

Program main fuction.

Physical memory file descriptor

Pointer to CM_PER registers

Pointer to CONTROL registers

Pointer to PWM0 registers

Pointer to PWM1 registers

Definition at line 142 of file check_config.c.

References CM_PER_BASE, CM_PER_SIZE, CONTROL_BASE, CONTROL_SIZE, EPWM_AQCTLA_OFFSET, EPWM_AQCTLB_OFFSET, EPWM_CMPA_OFFSET, EPWM_CMPB_OFFSET, EPWM_OFFSET, EPWM_TBCNT_OFFSET, EPWM_TBCTL_OFFSET, EPWM_TBPRD_OFFSET, EPWMSS0_CLKCTRL_OFFSET, EPWMSS1_CLKCTRL_OFFSET, EPWMSS2_CLKCTRL_OFFSET, L4LS_CLKCTRL_OFFSET, L4LS_CLKSTCTRL_OFFSET, PRU_ICSS_CLKCTRL_OFFSET, PWM0_BASE, PWM1_BASE, PWM_SIZE, PWMSS_CLKCONFIG_OFFSET, PWMSS_CLKSTATUS_OFFSET, PWMSS_CTRL_OFFSET, PWMSS_OFFSET, and PWMSS_SYSCONFIG_OFFSET.